- 您现在的位置:买卖IC网 > Sheet目录1212 > DS21Q55DK (Maxim Integrated Products)KIT DESIGN FOR DS21Q55

�� �

�

�

�DS21Q55DK� Quad� T1/E1/J1� Transceiver� Design� Kit�

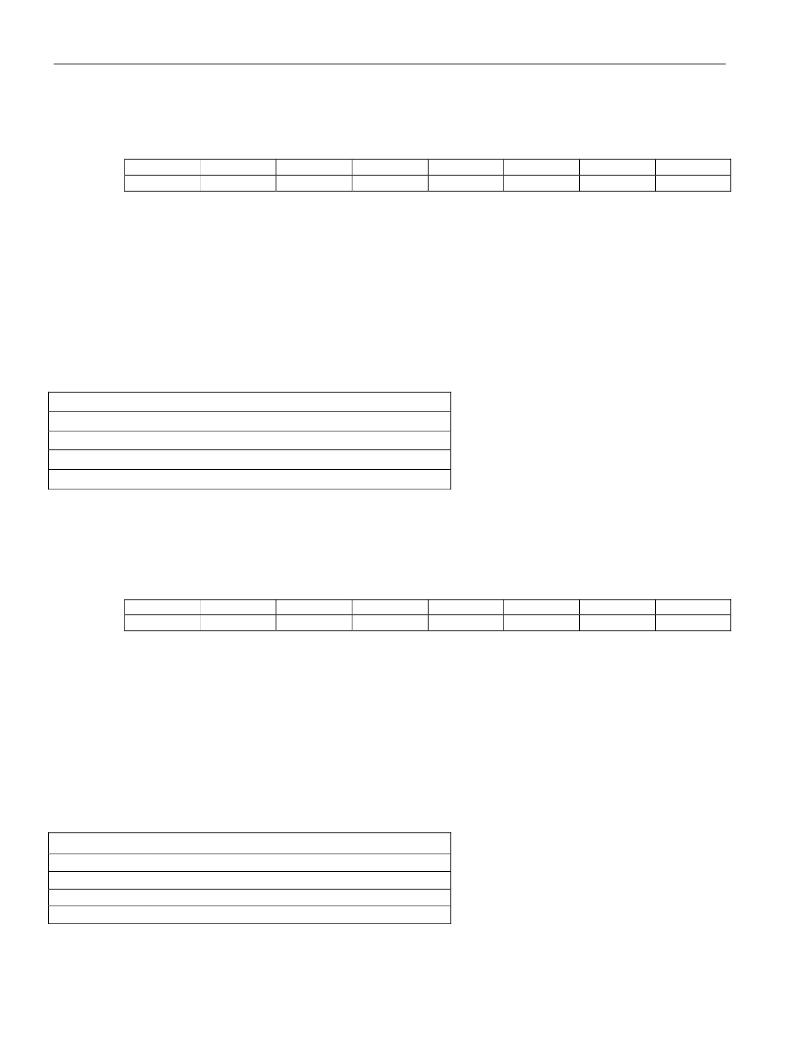

�Register� Name:� SYSCLKT�

�Register� Description:� DS21Q55� TSYSCLK� Pin� Setting�

�Register� Offset:� 0x0013�

�Bit� #�

�Name�

�Default�

�7�

�R4S1�

�0�

�6�

�R4S0�

�0�

�5�

�R3S1�

�0�

�4�

�R3S0�

�0�

�3�

�R2S1�

�0�

�2�

�R2S0�

�0�

�1�

�R1S1�

�0�

�0�

�R1S0�

�0�

�Bit� 0� to� 1:� DS21Q55� Port� 1� TSYSCLK� Source� (R1S0,� R1S1)�

��Bit� 2� to� 3:� DS21Q55� Port� 2� TSYSCLK� Source� (R2S0,� R2S1)�

��Bit� 4� to� 5:� DS21Q55� Port� 3� TSYSCLK� Source� (R3S0,� R3S1)�

��Bit� 6� to� 7:� DS21Q55� Port� 4� TSYSCLK� Source� (R4S0,� R4S1)�

��Table� 4.� TSYSCLKx� Source� Definition�

�RxS1,� RxS0�

�00�

�01�

�10�

�11�

�TSYSCLK� X� CONNECTION�

�Drive� TSYSCLK� X� with� the� 1.544MHz� clock�

�Drive� TSYSCLK� X� with� the� 2.048MHz� clock�

�Drive� TSYSCLK� X� with� 8.192MHz� clock�

�Drive� TSYSCLK� X� with� DS21Q55� Port� X� BPCLK�

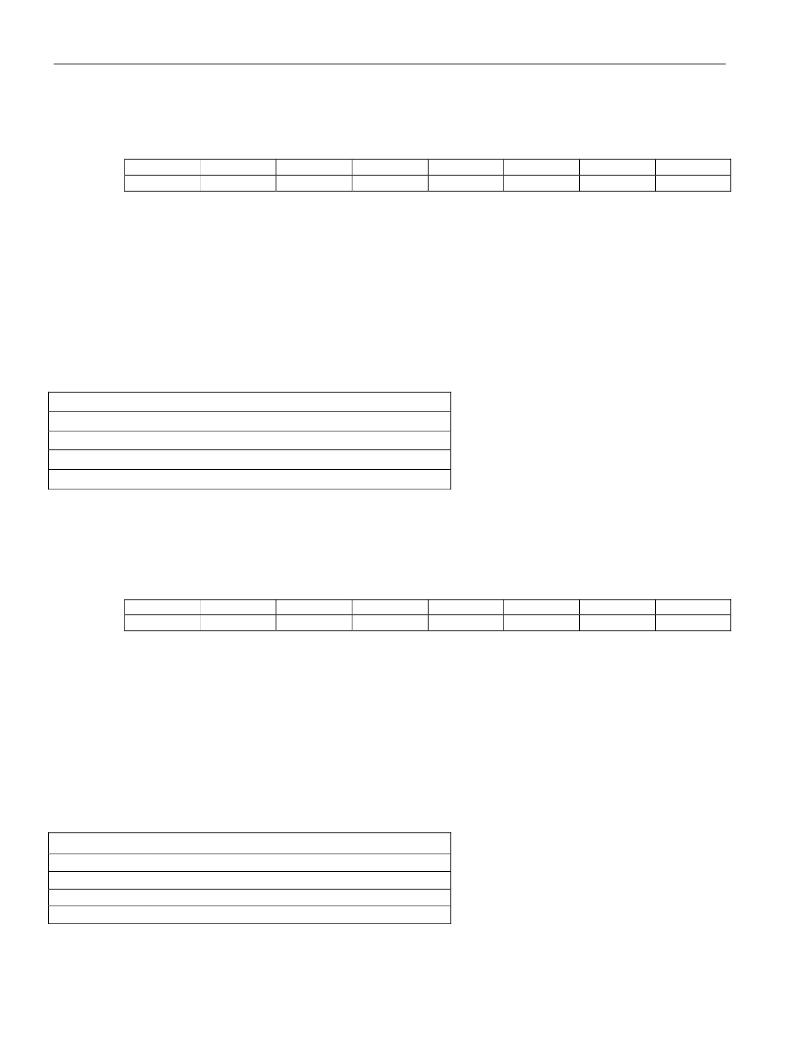

�Register� Name:� SYSCLKR�

�Register� Description:� DS21Q55� RSYSCLK� Pin� Setting�

�Register� Offset:� 0x0014�

�Bit� #�

�Name�

�Default�

�7�

�T4S1�

�0�

�6�

�T4S0�

�0�

�5�

�T3S1�

�0�

�4�

�T3S0�

�0�

�3�

�T2S1�

�0�

�2�

�T2S0�

�0�

�1�

�T1S1�

�0�

�0�

�T1S0�

�0�

�Bit� 0� to� 1:� DS21Q55� Port� 1� RSYSCLK� Source� (T1S0,� T1S1)�

��Bit� 2� to� 3:� DS21Q55� Port� 2� RSYSCLK� Source� (T2S0,� T2S1)�

��Bit� 4� to� 5:� DS21Q55� Port� 3� RSYSCLK� Source� (T3S0,� T3S1)�

��Bit� 6� to� 7:� DS21Q55� Port� 4� RSYSCLK� Source� (T4S0,� T4S1)�

��Table� 5.� RSYSCLKx� Source� Definition�

�TxS1,� TxS0�

�00�

�01�

�10�

�11�

�RSYSCLK� X� CONNECTION�

�Drive� RSYSCLK� X� with� the� 1.544MHz� clock�

�Drive� RSYSCLK� X� with� the� 2.048MHz� clock�

�Drive� RSYSCLK� X� with� 8.192MHz� clock�

�Drive� RSYSCLK� X� with� DS21Q55� Port� X� BPCLK�

�9� of� 32�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS2436K

KIT DEMO BATT ID/MON CHIP DS2436

DS2438K

KIT DEMO SMART BATT MON DS2438

DS26303DK

KIT DESIGN FOR DS26303

DS26502DK

KIT DESIGN FOR DS26502

DS26503DK

KIT DESIGN FOR DS26503

DS26504DK

KIT DESIGN FOR DS26504

DS26519DK

KIT DEMO FOR DS26519

DS26521DK

KIT DESIGN FOR DS26521

相关代理商/技术参数

DS21Q55N

制造商:未知厂家 制造商全称:未知厂家 功能描述:Quad T1/E1/J1 Transceiver

DS21Q58

制造商:DALLAS 制造商全称:Dallas Semiconductor 功能描述:E1 Quad Transceiver

DS21Q58L

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q58L+

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q58LN

功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q58LN+

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q59

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:RELIABILITY REPORT FOR DS21Q59, REV A2

DS21Q59DK

功能描述:网络开发工具 DS21Q59 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V